# 5 Port 10/100 Ethernet Integrated Switch

#### **Features**

- 5 port 10/100 Ethernet switch with built in transceivers and memory

- Build in SSRAM for frame buffer

- Built in storage of 1K MAC address

- Support flow control

- Support IEEE802.3x for flow control for full duplex mode operation

- Support backpressure for flow control for half duplex mode operation

- 5 port switching fabric

- Support two-level hashing algorithm to solve MAC address collision

- Support MAC address aging

- Store and forward mode

- Broadcast storm protection

- Full line speed capability of 148800 (14880) packets/sec for 100M (10M)

- Support 1536 byte data transfer for VLAN packet traffic

- Port base VLAN

- Port base CoS configuration

- Integrate 5 ports transceiver

- Each port can be auto negotiable or forced 10M/100M, full/half duplex

- Each port can be configured as 100BaseFX

- Automatic MDI/MDI-X configuration

- Support two MII, one SMI and extended MII registers for router application

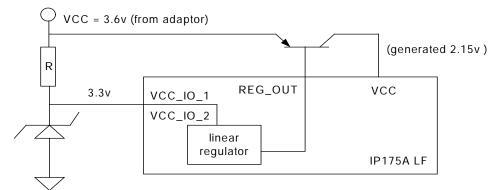

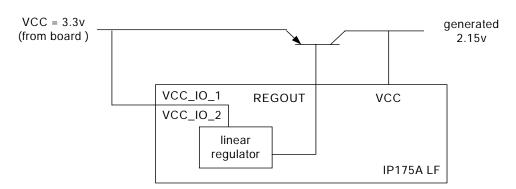

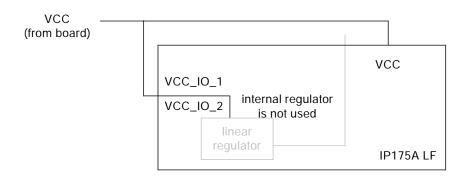

- Built in regulator for 3.3v to 2.15v

- LED status of Link, activity, Full/half duplex, speed, and power on diagnostic function

- Initial parameter setting by pin or EEPROM (24LC01) configuration

- Utilize single clock source (25Mhz)

- 0.25u technology

- Support Lead Free package (Please refer to the Order Information)

### **General Description**

IP175A LF is a low cost 10/100 Ethernet single chip switch. It integrates a 5-port switch controller, SSRAM, and 5 10/100 Ethernet transceivers. Each of the transceivers complies with the IEEE802.3, IEEE802.3u, and IEEE802.3x specifications. The transceivers are designed in DSP approach with 0.25um technology; they have high noise immunity and robust performance.

IP175A LF operates in store and forward mode. It supports flow control, auto MDI/MDI-X, CoS, port base VLAN, and LED functions, etc. Each port can be configured to auto-negotiation or forced 10M/100M, full/half duplex, and it is also able to configure to 100BaseFX transmission mode. Using an EEPROM or pull up/down resistors on specified pins can configure the desired options. IP175A LF does not support "forced 10M half mode".

IP175A LF supports two MII ports for router application, which supports 4 LAN ports and one WAN port. MII0 is for LAN traffic and MII1 is for WAN traffic and no external PHY is needed. Both MII can work in PHY mode and interface to the external MAC in this application. The external MAC can monitor or configure IP175A LF by accessing MII registers through SMI.

MII0 also can be configured to be MAC mode. It is used to interface an external PHY to work as a 4+1 switch.

1/60

### **Table Of Contents**

| Fea | itures.      |         |                                       | 1  |

|-----|--------------|---------|---------------------------------------|----|

| Ger | neral D      | escrip  | tion                                  | 1  |

| Tab | le Of C      | Conten  | ts                                    | 2  |

| Rev | ision l      | History |                                       | 3  |

|     |              |         |                                       |    |

|     |              |         | itinued)                              |    |

|     |              |         | itinued)                              |    |

|     |              | •       | ,                                     |    |

|     |              |         |                                       |    |

|     |              |         | ons                                   |    |

|     |              | •       | (continued)                           |    |

| Pin | Descr        | iptions | (continued)                           | 10 |

| Pin | Descr        | iptions | (continued)                           | 11 |

| Pin | Descr        | iptions | (continued)                           | 12 |

|     |              |         | (continued)                           |    |

|     |              | •       | · · · · · · · · · · · · · · · · · · · |    |

|     |              |         | (continued)                           |    |

|     |              |         | escription                            |    |

|     | 4.1          |         | switch application                    |    |

|     | 4.2<br>4.3   |         | applicationAC mode                    |    |

|     | 4.4          |         | Il and MII register                   |    |

|     | 4.5          |         | ort configuration                     |    |

|     | 4.6          |         | 5. 55 mgu 4.55                        |    |

|     | 4.7          |         |                                       |    |

|     | 4.7          | '.1     | Port base VLAN                        | 27 |

|     | 4.7          |         | Tag / un-tag                          |    |

|     | 4.8          |         | alue set by LED pins                  |    |

|     | 4.9          |         | regulator                             |    |

|     | 4.10         |         | ed MII registers                      |    |

|     | 4.11         |         | DM register                           |    |

|     | 4.12<br>4.13 |         | sic MII registers                     |    |

|     |              |         | ink Timmingaracteristics              |    |

|     |              |         |                                       |    |

|     | 5.1<br>5.2   |         | te Maximum Ratingaracteristic         |    |

|     |              |         | ing                                   |    |

|     | 5.3          |         | Reset Timing                          |    |

|     | 5.3          |         | MIIO PHY Mode Timing                  |    |

|     | 5.3          |         | MII1 PHY Mode Timing                  |    |

|     | 5.3          |         | MIIO MAC Mode Timing                  |    |

|     | 5.3          | 3.5     | SMI Timing                            | 58 |

|     | 5.3          |         | EEPROM Timing                         |    |

| 6   | Order        | Inform  | ation                                 | 59 |

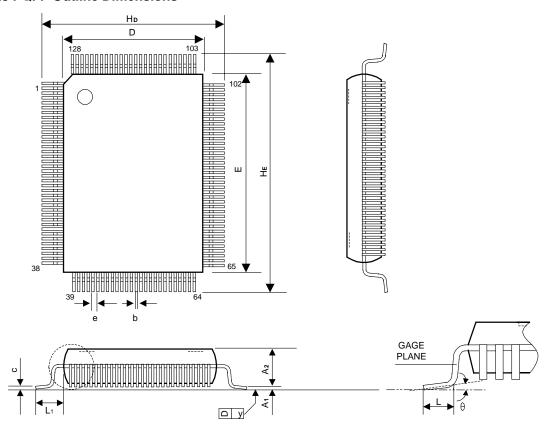

| 7   | Packa        | ge Det  | tail                                  | 60 |

## **Revision History**

| Revision #       | Change Description                                                                                                                                                         |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IP175A LF-DS-R01 | Initial release.                                                                                                                                                           |

| IP175A LF-DS-R02 | 1. Update pin description of REG_OUT on page 14. 2. Add VCC_IO limitation to the operation condition on page 61. 3. Add VCC_IO_1, VCC_IO_2, VCC pin description on page 18 |

| IP175A LF-DS-R03 | Update pin description of Reg_out page 14.                                                                                                                                 |

| IP175A LF-DS-R04 | Remove MII register 16H.                                                                                                                                                   |

| IP175A LF-DS-R05 | Remove VLAN from MII Register.                                                                                                                                             |

| IP175A LF-DS-R06 | 1. ADD AC Timing 2. Change minimum VCC from 2.1v to 2.0v on page 14 & 50                                                                                                   |

| IP175A LF-DS-R07 | Add the order information for lead free package.                                                                                                                           |

| IP175A LF-DS-R08 | ADD LED Blink Timing Table on page 52.                                                                                                                                     |

## 1 Applications

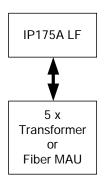

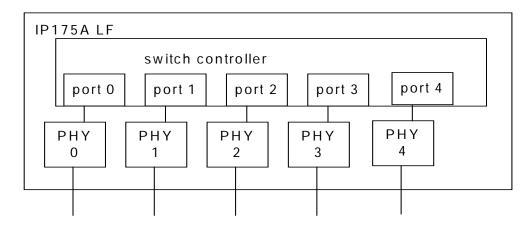

5 port Ethernet switch

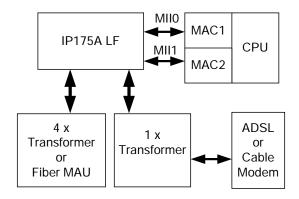

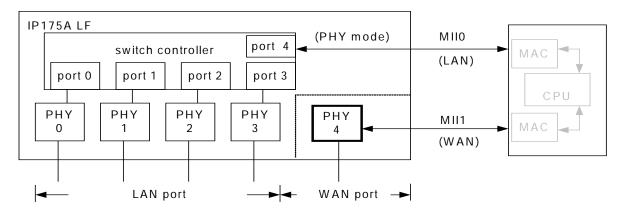

#### Application 2:

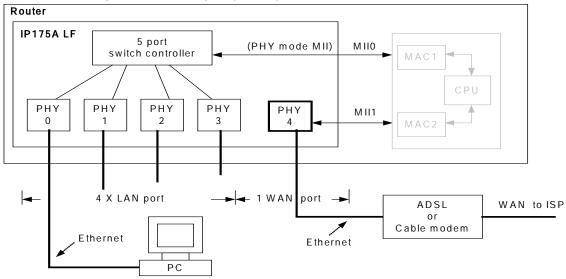

4 LAN port + one WAN port (Router)

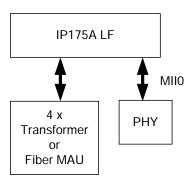

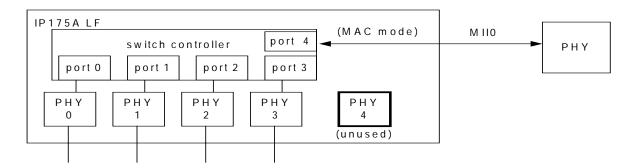

### Application 3:

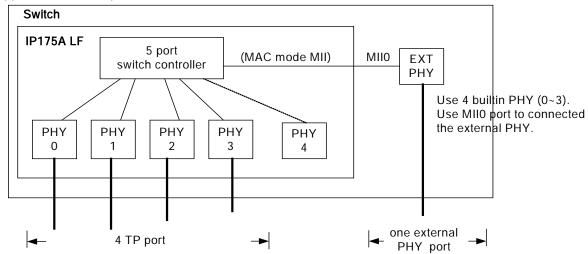

4 TP ports + one external PHY

### Applications (continued)

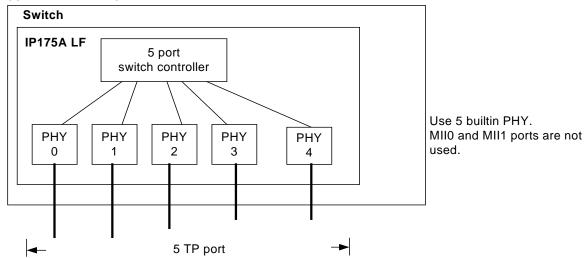

### Application 1: 5 TP port switch

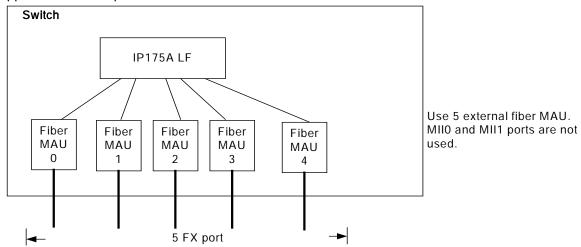

### Application 1: 5 FX port switch

### Applications (continued)

### Application 2: 4 LAN port + one WAN port (Router)

### Application 3: 4 TP port + one external PHY

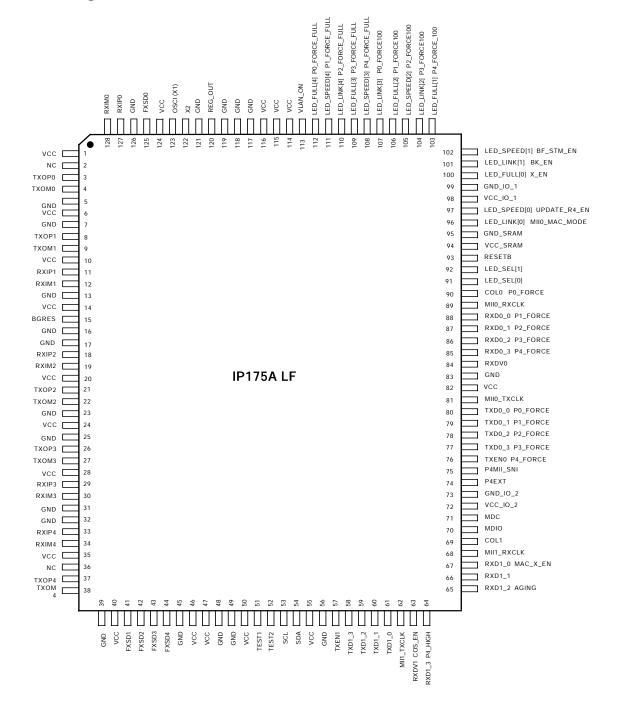

### 2 Pin Diagram

## 3 Pin Descriptions

| Туре | Description                       |  |  |  |  |  |

|------|-----------------------------------|--|--|--|--|--|

| I    | Input pin                         |  |  |  |  |  |

| 0    | Output pin                        |  |  |  |  |  |

| IPL  | Input pin with internal pull low  |  |  |  |  |  |

| IPH  | Input pin with internal pull high |  |  |  |  |  |

| Туре | Description                                  |

|------|----------------------------------------------|

| IPL1 | Input pin with internal pull low 22.8k ohm   |

| IPH1 | Input pin with internal pull high 22.8k ohm  |

| IPL2 | Input pin with internal pull low 92.6k ohm   |

| IPH2 | Input pin with internal pull high 113.8k ohm |

| Pin no.  | Label                                              | Туре | Description                                                                                                                                                                                                                                                     |  |  |  |

|----------|----------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| LED pins | LED pins used as initial setting mode during reset |      |                                                                                                                                                                                                                                                                 |  |  |  |

| 102      | BF_STM_EN                                          | IPL1 | Broadcast storm protection enable 1: enable, 0: disable (default)                                                                                                                                                                                               |  |  |  |

| 101      | BK_EN                                              | IPH1 | Backpressure enable 1: enable (default), 0: disable  This pin doesn't set the flow control of MII0 port. MAC_X_EN sets the flow control of MII0 port.                                                                                                           |  |  |  |

| 100      | X_EN                                               | IPH1 | IEEE802.3X enable 1: enable (default), 0: disable  This pin doesn't set the flow control of MII0 port. MAC_X_EN sets the flow control of MII0 port.                                                                                                             |  |  |  |

| 97       | UPDATE_R4_EN                                       | IPL1 | Change capability enable A full duplex port will change its capability to half duplex, if the remote full duplex port does not support IEEE802.3x then this function is enabled. It should be pulled low for normal operation.  1: enable, 0: disable (default) |  |  |  |

| Pin no.    | Label                                              | Туре | Description                                                                                                                                                                                                                                                                                                            |  |  |  |

|------------|----------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MII pins u | MII pins used as initial setting mode during reset |      |                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 113        | VLAN_ON                                            | IPL  | VLAN enable 1: enable, 0: disable (default)  IP175A LF is separated into 4 VLAN groups if this function is enabled. VLAN 1: port0, port 4; VLAN 2: port 1, port 4; VLAN 3: port 2, port 4; VLAN 4: port 3, port 4; Programming EEPROM registers 0Eh~12h or MII register 13h~15h will overwrite the VLAN configuration. |  |  |  |

| 64         | P4_HIGH                                            | IPL2 | Port4 is set to be high priority port 1: enable, 0: disabled (default)  Packets received from port4 are handled as high priority packets if the feature is enabled. Please refer to EEPROM registers 0Eh~12h or MII register 13h~15h for detail information.                                                           |  |  |  |

| 63         | COS_EN                                             | IPL2 | Class of service enable 1: enable, 0: disabled (default)  Packets with high priority tag are handled as high priority packets for all ports if the feature is enabled. Please refer to EEPROM registers 0Eh~12h or MII register 13h~15h for detail information.                                                        |  |  |  |

| 65         | AGING                                              | IPH2 | Address aging enable 1: enable, aging time 300s (default), 0: disable                                                                                                                                                                                                                                                  |  |  |  |

| Pin no.    | Label             | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------|-------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| External I | VIII port setting |      |                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 74         | P4EXT             | IPL  | <ul> <li>External MII port enable</li> <li>1: Both MII interface are enabled for router application. MII1 supports PHY mode only. MII1 interfaces to internal PHY4 of IP175A LF. It is connected to an external MAC device. MII0 supports both PHY mode and MAC mode depending on the setting of MII0_MAC_MOD (pin 96).</li> <li>0: External MII interface is disabled and IP175A LF works as a 5-port switch (default).</li> </ul> |

| 75         | P4MII_SNI         | IPL  | External MII interface selection  1: SNI interface IP175A LF supports PHY mode SNI (MII0_MAC_MOD=0), i.e., it can be connected to an external MAC. IP175A LF doesn't support MAC mode SNI (MII0_MAC_MOD=1), i.e., it should not be connected to an external PHY.  0: MII interface (default).                                                                                                                                       |

| Pin no.    | Label               | Туре  | Description                                                                                                                                                                                                               |

|------------|---------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| External I | MII0 interface (P4E | XT=1) |                                                                                                                                                                                                                           |

| 67         | MAC_X_EN            | IPH2  | Flow control enable for external MII0 port 1: enable (default), 0: disable                                                                                                                                                |

| 96         | MII0_MAC_MOD        | IPL1  | External MII0 port MAC mode  1: MII0 works as a MAC and should be connected to an external PHY.  0: MII0 works as a PHY and should be connected to an external MAC device (default).  This pin does not affect MII1 port. |

| 71, 70     | MDC, MDIO           | IPL   | SMI The external MAC device uses the interface to program basic and extended MII register to configure PHY 4 and switch controller,                                                                                       |

| Pin no.           | Label                          | Туре  | Description                                                                                           |

|-------------------|--------------------------------|-------|-------------------------------------------------------------------------------------------------------|

| External I        | VIII0 interface (PHY           | mode, | , MII0_MAC_MOD=0, P4MII_SNI=0)                                                                        |

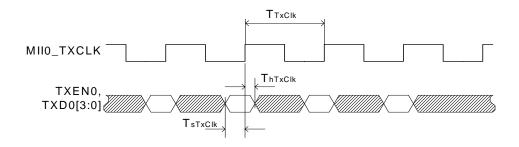

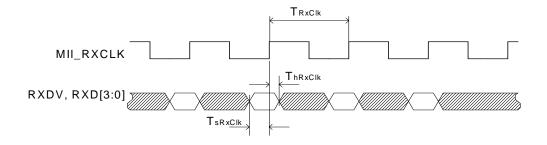

| 81                | MII0_TXCLK                     | 0     | MII transmit clock                                                                                    |

| 80, 79,<br>78, 77 | TXD0_0, TXD0_1, TXD0_2, TXD0_3 | IPL2  | MII transmit data                                                                                     |

|                   |                                |       | It is sampled at the rising edge of MII0_TXCLK.                                                       |

| 76                | TXEN0                          | IPL2  | MII transmit enable                                                                                   |

|                   |                                |       | It is used to frame TXD0[3:0]. It is sampled at the rising edge of MII0_TXCLK.                        |

| 90                | COL0                           | 0     | MII collision                                                                                         |

|                   |                                |       | It is active when port 4 of switch controller is set to be half duplex and a collision event happens. |

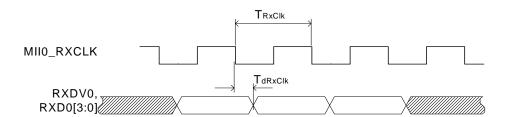

| 84                | RXDV0                          | 0     | MII receive data valid                                                                                |

|                   |                                |       | It is used to frame RXD0[3:0]. It is sent out at the falling edge of MII0_TXCLK.                      |

| 88, 87,           | RXD0_0, RXD0_1,                | 0     | MII receive data                                                                                      |

| 86, 85            | RXD0_2, RXD0_3                 |       | It is sent out at the falling edge of MII0_TXCLK.                                                     |

| 89                | MII0_RXCLK                     | 0     | MII receive clock                                                                                     |

|                   |                                |       | There is no clock output in this mode.                                                                |

| Pin no.    | Label               | Туре   | Description                                                                                                           |

|------------|---------------------|--------|-----------------------------------------------------------------------------------------------------------------------|

| External I | MII0 interface (MAC | C mode | , MII0_MAC_MOD=1, P4MII_SNI=0)                                                                                        |

| 81         | MII0_TXCLK          | I      | MII transmit clock                                                                                                    |

|            |                     |        | It is an input clock and it is connected to MII_TXCLK of external PHY.                                                |

| 80, 79,    | TXD0_0, TXD0_1,     | 0      | MII transmit data                                                                                                     |

| 78, 77     | TXD0_2, TXD0_3      |        | It is connected to MII_TXD of external PHY. It is sent out at the rising edge of MII0_TXCLK.                          |

| 76         | TXEN0               | 0      | MII transmit enable                                                                                                   |

|            |                     |        | It is an output signal and is connected to MII_TXEN of external PHY. It is sent out at the rising edge of MII0_TXCLK. |

| 90         | COL0                | IPL2   | MII collision                                                                                                         |

|            |                     |        | It is an input signal and is connected to the MII_COL of external PHY.                                                |

| 84         | RXDV0               | I      | MII receive data valid                                                                                                |

|            |                     |        | It is an input signal and is connected to the MII_RXDV of external PHY. RXDV0 is used to frame RXD0[3:0].             |

| 88, 87,    | RXD0_0, RXD0_1,     | I      | Receive data                                                                                                          |

| 86, 85     | RXD0_2, RXD0_3      |        | It is NRZ data and is connected MII_RXD[3:0] of external PHY. It is received at the rising edge of MII0_RXCLK.        |

| 89         | MII0_RXCLK          | Ι      | MII receive clock                                                                                                     |

| Pin no.           | Label                             | Туре   | Description                                                                      |

|-------------------|-----------------------------------|--------|----------------------------------------------------------------------------------|

| External I        | WII1 interface (PH)               | / mode | only, P4EXT=1)                                                                   |

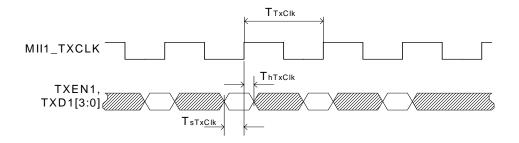

| 62                | MII1_TXCLK                        | 0      | MII Transmit clock                                                               |

| 61, 60,<br>59, 58 | TXD1_0, TXD1_1, TXD1_2, TXD1_3    | IPL2   | MII transmit data                                                                |

|                   |                                   |        | It is sampled at the rising edge of MII1_TXCLK.                                  |

| 57                | TXEN1                             | IPL2   | MII transmit enable                                                              |

|                   |                                   |        | It is used to frame TXD1[3:0]. It is sampled at the rising edge of MII1_TXCLK.   |

| 69                | COL1                              | 0      | MII collision                                                                    |

|                   |                                   |        | It is active when PHY4 is set to be half duplex and a collision event happens.   |

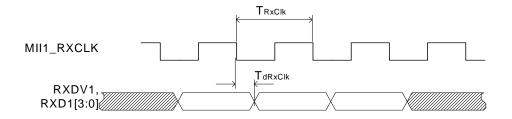

| 63                | RXDV1                             | 0      | MII receive data valid                                                           |

|                   |                                   |        | It is used to frame RXD1[3:0]. It is sent out at the falling edge of MII1_RXCLK. |

| 67, 66,<br>65, 64 | RXD1_0, RXD1_1,<br>RXD1_2, RXD1_3 | 0      | MII receive data                                                                 |

|                   | _ ,                               |        | It is sent out at the falling edge of MII1_RXCLK.                                |

| 68                | MII1_RXCLK                        | 0      | MII receive clock                                                                |

| Pin no.  | Label      | Туре | Description                                                                                                                         |  |  |  |  |

|----------|------------|------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Force mo | Force mode |      |                                                                                                                                     |  |  |  |  |

| 85       | P4_FORCE   | IPL2 | Port4 works at force mode.  1: force mode, disable port4 NWAY capability  0: auto-negotiation with all capability enabled (default) |  |  |  |  |

| 76       |            |      | It is used to force MII0 port PHY mode if P4EXT is pulled high.                                                                     |  |  |  |  |

|          |            |      | It's set by pin 85 if MII0 is in PHY mode and it's set by pin 76 if MII0 is in MAC mode.                                            |  |  |  |  |

| 86       | P3_FORCE   | IPL2 | Port3 works at force mode.  1: force mode, disable port3 NWAY capability  0: auto-negotiation with all capability enabled (default) |  |  |  |  |

| 77       |            |      | o. auto-negotiation with all capability enabled (default)                                                                           |  |  |  |  |

|          |            |      | It's set by pin 86 if MII0 is in PHY mode and it's set by pin 77 if MII0 is in MAC mode.                                            |  |  |  |  |

| 87       | P2_FORCE   | IPL2 | Port2 works at force mode.  1: force mode, disable port2 NWAY capability                                                            |  |  |  |  |

| 78       |            |      | 0: auto-negotiation with all capability enabled (default)                                                                           |  |  |  |  |

|          |            |      | It's set by pin 87 if MII0 is in PHY mode and it's set by pin 78 if MII0 is in MAC mode.                                            |  |  |  |  |

| 88       | P1_FORCE   | IPL2 | Port1 works at force mode.  1: force mode, disable port1 NWAY capability                                                            |  |  |  |  |

| 79       |            |      | 0: auto-negotiation with all capability enabled (default)                                                                           |  |  |  |  |

| 173      |            |      | It's set by pin 88 if MII0 is in PHY mode and it's set by pin 79 if MII0 is in MAC mode.                                            |  |  |  |  |

| 90       | P0_FORCE   | IPL2 | Port0 works at force mode.  1: force mode, disable port0 NWAY capability  0: auto-negotiation with all capability enabled (default) |  |  |  |  |

| 80       |            |      | o. auto-negotiation with all capability enabled (default)                                                                           |  |  |  |  |

|          |            |      | It's set by pin 90 if MII0 is in PHY mode and it's set by pin 80 if MII0 is in MAC mode.                                            |  |  |  |  |

| Pin no.  | Label       | Туре | Description                                                                                                                  |

|----------|-------------|------|------------------------------------------------------------------------------------------------------------------------------|

| Force mo | de          |      |                                                                                                                              |

| 103      | P4_FORCE100 | IPL1 | Force port4 work at 100M or 10M.  1: force 100M  0: force 10M (default)  It is used to force MII0 port PHY mode if P4EXT =1. |

| 104      | P3_FORCE100 | IPL1 | Force port3 work at 100M or 10M. 1: force 100M 0: force 10M (default)                                                        |

| 105      | P2_FORCE100 | IPL1 | Force port2 work at 100M or 10M. 1: force 100M 0: force 10M (default)                                                        |

| 106      | P1_FORCE100 | IPL1 | Force port1 work at 100M or 10M. 1: force 100M 0: force 10M (default)                                                        |

| 107      | P0_FORCE100 | IPL1 | Force port0 work at 100M or 10M. 1: force 100M 0: force 10M (default)                                                        |

| Pin no.  | Label         | Туре | Description                                                                                                                                                                                                |

|----------|---------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Force mo | de            |      |                                                                                                                                                                                                            |

| 108      | P4_FORCE_FULL | IPL1 | Force port4 work at full duplex or half duplex  1: force full duplex  0: force half duplex (default)  It is used to force MII0 port PHY mode if P4EXT=1. IP175A LF does not support "force 10M half mode". |

| 109      | P3_FORCE_FULL | IPL1 | Force port3 work at full duplex or half duplex 1: force full duplex 0: force half duplex (default) IP175A LF does not support "force 10M half mode".                                                       |

| 110      | P2_FORCE_FULL | IPL1 | Force port2 work at full duplex or half duplex 1: force full duplex 0: force half duplex (default) IP175A LF does not support "force 10M half mode".                                                       |

| 111      | P1_FORCE_FULL | IPL1 | Force port1 work at full duplex or half duplex 1: force full duplex 0: force half duplex (default) IP175A LF does not support "force 10M half mode".                                                       |

| 112      | P0_FORCE_FULL | IPL1 | Force port0 work at full duplex or half duplex 1: force full duplex 0: force half duplex (default) IP175A LF does not support "force 10M half mode".                                                       |

| Pin no.                                                | Label                                                                                            | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|--------------------------------------------------------|--------------------------------------------------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Transceiv                                              | ver                                                                                              |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 127,<br>128,<br>11, 12,<br>18,19,<br>29, 30,<br>33, 34 | RXIP0, RXIM0,<br>RXIP1, RXIM1,<br>RXIP2, RXIM2,<br>RXIP3, RXIM3,<br>RXIP4, RXIM4                 | I    | TP receive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 3, 4,<br>8, 9,<br>21, 22,<br>26, 27,<br>37, 38         | TXOP0,<br>TXOM0,<br>TXOP1,<br>TXOM1,<br>TXOP2,<br>TXOM2,<br>TXOP3,<br>TXOP3,<br>TXOP4,<br>TXOP4, | 0    | TP transmit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 14                                                     | BGRES                                                                                            | 0    | Band gap resister. It is connected to GND through a 6.2 k ohms resistor. Please refer to application circuit for more information.                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 125, 41,<br>42, 43,<br>44                              | FXSD0~4                                                                                          | I    | IP175A LF will latch the value on FXSDx pins at the end of reset to decide if the port works at 100BaseFX mode. A port works in 100BaseFX mode, if its corresponding signal FXSDx > 0.6v at the end of reset. FXSDx should be connected to GND if the port works in TP mode. That is, a port is a fiber port if its FXSDx is connected to the SD of fiber MAU and a port is a TP port if its FXSDx is connected to GND.  The SD of fiber port is active if the voltage of FXSDx is higher than 1.2v. It is used to inform IP175A LF if the fiber is plugged or not. |  |  |  |

| Pin no. | Label Type |   | Description            |

|---------|------------|---|------------------------|

| Misc.   |            |   |                        |

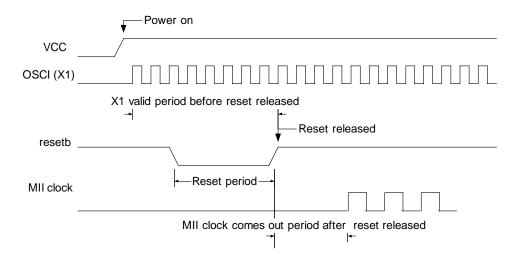

| 123     | X1         | 1 | 25M system clock input |

| 122     | X2         | 0 | Crystal pin            |

| 93      | RESETB     | I | Reset, low active      |

| Pin no. | Label   | Туре | Description                                                                                                                                                                                                                                                                                                                   |

|---------|---------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Misc.   |         |      |                                                                                                                                                                                                                                                                                                                               |

| 120     | REG_OUT | 0    | Regulator output                                                                                                                                                                                                                                                                                                              |

|         |         |      | It is used to control external transistor to generate a 2.15v ±5% voltage source when VCC_IO_1 and VCC_IO_2 are exactly 3.3v and all ports are link on. To meet the specification of minimum VCC (2.0v), VCC_IO_1 and VCC_IO_2 should be at least 3.3v. The supply current of external transistor used should be at least 1A. |

| Pin no. | Label | Туре                                                                                                                                                                                                                     | Description                                                                                             |

|---------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| EEPROM  |       |                                                                                                                                                                                                                          |                                                                                                         |

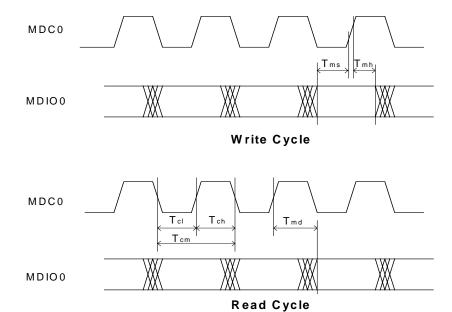

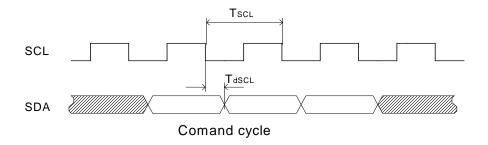

| 53      | SCL   | I/O After reset, it is used as clock pin SCL of EEPROM. Its period longer than 10us. IP175A LF stops reading EEPROM if it fit there is no 55AA pattern in register 0. After reading EEPRO this pin becomes an input pin. |                                                                                                         |

| 54      | SDA   | Ю                                                                                                                                                                                                                        | After reset, it is used as data pin SDA of EEPROM. After reading EEPROM, this pin becomes an input pin. |

| Pin no.                          | Label          | Туре | Description                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------|----------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LED                              |                |      |                                                                                                                                                                                                                                                                                                                                                                             |

| 92, 91                           | LED_SEL[1:0]   | IPH  | LED output mode selection.                                                                                                                                                                                                                                                                                                                                                  |

|                                  |                |      | LED_SEL[1:0]=00: LED mode 0,<br>LED_SEL[1:0]=01: LED mode 1,<br>LED_SEL[1:0]=10: LED mode 2,<br>LED_SEL[1:0]=11: LED mode 3 (default)                                                                                                                                                                                                                                       |

| 110,<br>107,<br>104,<br>101, 96  | LED_LINK[4:0]  | 0    | Link, Activity (output after reset) LED mode0: 100M Link + Activity (same as mode 2) LED mode1: Receive activity (1: not receiving, flash: receiving) LED mode2, 100M Link + Activity (1: 100M Link fail, 0: 100M Link ok and no activity, flash: 100M Link ok and TX/RX activity) LED mode3: Link + Activity (1: link fail, 0: link ok, flash: Link ok and TX/RX activity) |

| 111,<br>108,<br>105,<br>102, 97  | LED_SPEED[4:0] | 0    | Speed (output after reset) LED mode0: (1: no collision, flash: collision) (note*) LED mode1: (1: speed=10M, 0: speed=100M) LED mode2: Full/half: (1: half, 0: full, flash: collision) LED mode3: (1: speed=10M, 0: speed=100M)                                                                                                                                              |

| 112,<br>109,<br>106,<br>103, 100 | LED_FULL[4:0]  | 0    | Full/half, Link (output after reset) LED mode0, 10M Link + Activity (same as mode 2) LED mode1, Link: (1: Link fail, 0: Link ok) LED mode2, 10M Link + Activity (1: 10M Link fail, 0: 10M Link ok and no activity, flash: 10M Link ok and TX/RX activity) LED mode3: Full/half: (1: half, 0: full, flash: collision)                                                        |

Note: LED\_SPEED[0] shows collision information for all ports. LED\_SPEED[4:1] is undefined.

| Pin no. | Label                 | Туре | Description                                                                                                                                                                                                                                 |

|---------|-----------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power   |                       |      |                                                                                                                                                                                                                                             |

| 98, 72  | VCC_IO_1,<br>VCC_IO_2 | I    | Power for output pins They should be connected 3.3v if MII, EEPROM, or built in regulator (REG_OUT) is used. They can be connected to the same power source as VCC if IP175A LF works as a 5-port switch without using bulilt in regulator. |

|         | VCC                   | I    | Power for core<br>2.15v~2.625v                                                                                                                                                                                                              |

| Pin no.  | n no. Label  |     | Description                                                               |

|----------|--------------|-----|---------------------------------------------------------------------------|

| Test mod | е            |     |                                                                           |

| 51, 52   | TEST1, TEST2 | IPL | Test mode selection They should be connected to GND for normal operation. |

### 4 Functional Description

### 4.1 5-port switch application

IP175A LF works as a 5 TP port auto MDI-MDIX switch when all fibers and MII function are disabled. In this case, both FXSDx and P4EXT should be pulled low. Each port can be with auto-negotiation or force mode in this application.

An example to illustrate the configuration setting of port4 when P4EXT is pulled low and MII is disabled

| Port | TP | FX | Nway | Capability     | FXSD4  | P4_FORCE | P4_FORCE100 | P4_FORCE_FULL |

|------|----|----|------|----------------|--------|----------|-------------|---------------|

| 4    | V  |    | V    | All capability | 0      | 0        | 0           | 0             |

| 4    | V  |    | V    | 10M/ full      | 0      | 1        | 0           | 1             |

| 4    | V  |    |      | 100M/ half     | 0      | 1        | 1           | 0             |

| 4    | V  |    | V    | 100M/ full     | 0      | 1        | 1           | 1             |

| 4    |    | V  |      | 100M half      | > 0.6v | 1        | 1           | 0             |

| 4    |    | V  |      | 100M full      | > 0.6v | 1        | 1           | 1             |

#### Note:

- 1. The configuration not in the table is inhibited.

- 2. "--": Not applicable

#### 4.2 Router application

IP175A LF supports two MII ports, MII0 and MII1, for router application when P4EXT is pulled high. Pin P4\_FORCE, P4\_FORCE100 and P4\_FORCE\_FULL decide the speed and duplex of MII0. The speed and duplex of MII1 depend on the result of auto-negotiation of PHY4. But, programming basic MII registers through SMI can modify them. MAC\_X\_EN pin decides the flow control option of MII0. It is illustrated in the following table.

| MIIO  |          |          |             |               |       |             |              |

|-------|----------|----------|-------------|---------------|-------|-------------|--------------|

| P4EXT | MAC_X_EN | P4_FORCE | P4_FORCE100 | P4_FORCE_FULL | Speed | Duplex      | Flow control |

| 0     | Х        | X        | X           | X             | М     | II0 disable | d.           |

| 1     | 0        | 1        | 1           | 1             | 100M  | Full        | Off          |

| 1     | 0        | 1        | 1           | 0             | 100M  | Half        | Off          |

| 1     | 0        | 1        | 0           | 1             | 10M   | Full        | Off          |

| 1     | 0        | 1        | 0           | 0             | 10M   | Half        | Off          |

| 1     | 1        | 1        | 1           | 1             | 100M  | Full        | On           |

| 1     | 1        | 1        | 1           | 0             | 100M  | Half        | On           |

| 1     | 1        | 1        | 0           | 1             | 10M   | Full        | On           |

X: "don't care"

IP175A LF can work as a router with 4 LAN ports and one WAN port, which use internal PHY (PHY4). MII0 is the interface between port4 of internal switch controller and external MAC. MII1 is the interface between internal transceiver PHY4 and external MAC. The switch controller forwards frames from port0~3 to MII0 and vice versa. PHY4 works as an independent single PHY for external MAC. MII0 works at PHY mode in this application (MII\_MAC\_MOD=0).

#### 4.3 MII0 MAC mode

MII0 works at MAC mode if MII\_MAC\_MOD is pulled high. MII0 is an interface between port4 of internal switch controller and external PHY. It replaces an Ethernet PHY with a user specified PHY in this application.

The speed and duplex of MII0 are configured by P4\_FORCE, P4\_FORCE100 and P4\_FORCE\_FULL. IP175A LF doesn't read the status of external PHY via SMI at this mode.

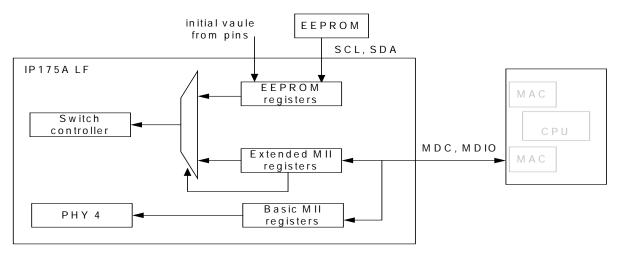

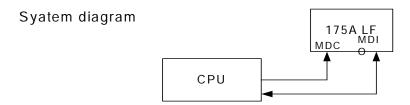

#### 4.4 MII, SMI and MII register

IP175A LF supports two MII and one SMI (MDC and MDIO). Two MII interface to the external MAC for data transfer and the SMI is used to program switch controller and PHY4.

IP175A LF provides basic MII registers for PHY4 and extended MII registers for switch controller. The external MAC monitors or configures PHY4 by reading or writing the basic MII registers through SMI. The external MAC monitors or configures switch controller by reading or writing the extended MII registers through SMI.

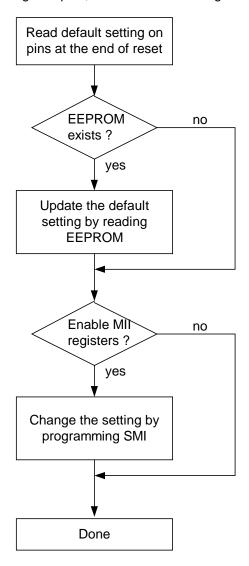

The switch controller can be configured by pin and EEPROM, too. The operation is illustrated in the following diagrams.

Three ways to configure IP175A, by pins, EEPROM, or programming MII registers

Parameter setting with pins, EEPROM and MII registers in IP175A LF

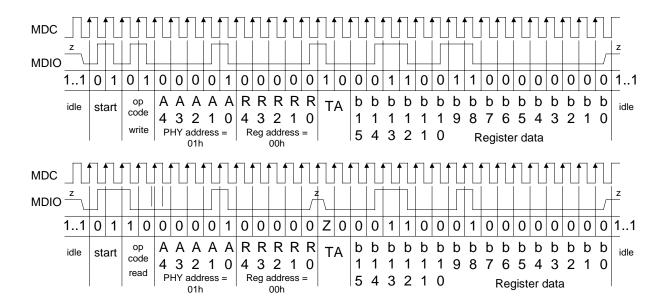

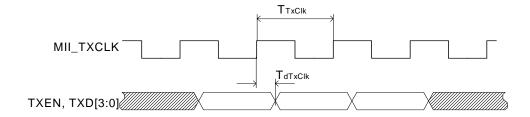

#### Serial management interface (SMI)

User can access IP175A LF's MII registers through serial management interface with pin MDC and MDIO. A specific pattern on MDIO is used to access a MII register. Its format is shown in the following table. When the SMI is idle, MDIO is in high impedance. To initialize the MDIO interface, the management entity sends a sequence of 32 contiguous "1" and "start" on MDIO.

| Frame format    | <ld><ldle><start><op code=""><phy address=""><registers address=""><turnaround><idle></idle></turnaround></registers></phy></op></start></ldle></ld>                                                                                                                                                                                                                                                                                                           |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read Operation  | <pre><idle>&lt;01&gt;&lt;10&gt;<a<sub>4A<sub>3</sub>A<sub>2</sub>A<sub>1</sub>A<sub>0</sub>&gt;<r<sub>4R<sub>3</sub>R<sub>2</sub>R<sub>1</sub>R<sub>0</sub>&gt;<z0></z0></r<sub></a<sub></idle></pre> <b<sub>15 b<sub>14</sub> b<sub>13</sub> b<sub>12</sub> b<sub>11</sub> b<sub>10</sub> b<sub>9</sub> b<sub>8</sub> b<sub>7</sub> b<sub>6</sub> b<sub>5</sub> b<sub>4</sub> b<sub>3</sub> b<sub>2</sub> b<sub>1</sub>b<sub>0</sub>&gt;<idle></idle></b<sub> |

| Write Operation | <idle>&lt;01&gt;&lt;01&gt;<a<sub>4A<sub>3</sub>A<sub>2</sub>A<sub>1</sub>A<sub>0</sub>&gt;<r<sub>4R<sub>3</sub>R<sub>2</sub>R<sub>1</sub>R<sub>0</sub>&gt;&lt;10&gt;<br/><b<sub>15 b<sub>14</sub> b<sub>13</sub> b<sub>12</sub> b<sub>11</sub> b<sub>10</sub> b<sub>9</sub> b<sub>8</sub> b<sub>7</sub> b<sub>6</sub> b<sub>5</sub> b<sub>4</sub> b<sub>3</sub> b<sub>2</sub> b<sub>1</sub>b<sub>0</sub>&gt;<idle></idle></b<sub></r<sub></a<sub></idle>       |

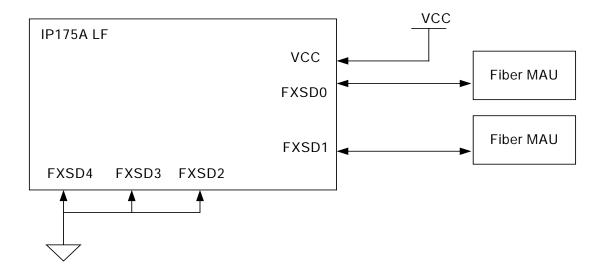

### 4.5 Fiber port configuration

Each port of IP175A LF can be configured to be a fiber port or a TP port. A port becomes a fiber port if its FXSDx is connected to a fiber MAU or it is pulled high. A port becomes a TP port if its FXSDx is pulled low. It is illustrated in the following table.

|                  |         | Port configuration |                     |                 |  |  |  |

|------------------|---------|--------------------|---------------------|-----------------|--|--|--|

| Voltage on FXSDx | TP port | Fiber port         | Fiber signal detect | Condition       |  |  |  |

| < 0.6v           | V       |                    |                     |                 |  |  |  |

| > 0.6v, < 1.2v   |         | V                  | Off                 | Fiber unplugged |  |  |  |

| > 1.2v           |         | V                  | On                  | Fiber plugged   |  |  |  |

The following is an example that IP175A LF is configured to be 3 TP ports and 2 fiber ports. In this case, the speed and duplex of fiber ports are defined by pin P0\_FORCE100, P0\_FORCE\_FULL, P1\_FORCE100, and P1\_FORCE\_FULL.

#### 4.6 CoS

IP175A LF supports two type of Cos. One is port base priority function and the other is frame base priority function. IP175A LF supports two levels of priority queues. A high priority packet will be queued in the memory as a high priority queue, this action will ensure more bandwidth for the high priority packets in the transmission.

The packets received from high priority port will be handled as high priority frames if the port base priority is enabled. It is enabled by programming the corresponding bit in EEPROM register 0Eh~12h of or MII register 13h~15h. Each port of IP175A LF can be configured as a high priority port individually.

IP175A LF examines the specific bits of VLAN tag and TCP/IP TOS for priority frames if the frame base priority is enabled. The packets will be handled as high priority frames if the value of VLAN tag or TCP/IP TOS field meets the high priority requirement. It is enabled by programming the corresponding bit in EEPROM register 16H~21H or MII register 17h~1Ch. The frame base priority function of each port can be enabled individually.

The Cos function can be active even if there is no EEPROM. IP175A LF supports an easy way to enable a sub set CoS function without EEPROM. Port 4 can be set as a high priority port if pin 64 (p4\_high) is pulled high. Frame base priority function of all ports is enabled if pin 63 (Cos\_en) is pulled high. The setting in register takes precedence of the setting on pins.

#### 4.7 VLAN

#### 4.7.1 Port base VLAN

IP175A LF supports port base VLAN functions. It separates IP175A LF into some groups (VLAN). A port is limited to communicate with other ports within the same group when the function is enabled. Frames are limited in a VLAN group and will not transmit out of this VLAN group. A port can be assigned to one or more VLAN groups. The members (ports) of a VLAN group are assigned by programming EEPROM register 0Eh~12h of or MII register 13h~15h.

The VLAN function can be active even if there is no EEPROM. IP175A LF supports an easy way to enable a sub set VLAN function without EEPROM. A default configuration of VLAN is adopted if pin 113 (VLAN\_on) is pulled high. The VLAN group in this mode is illustrated in the pin description of VLAN\_on. It is benefit in a router application that an individual LAN port can shares a WAN port. The setting in register takes precedence of the setting on pins.

### 4.7.2 Tag / un-tag

IP175A LF supports tag / un-tag functions. When the function is enabled, IP175A LF inserts the pre-defined tag into a forwarded frame if the frame is forwarded to a tagged field. IP175A LF strips the tag of a frame if the frame is forwarded to an untagged field. The operation is illustrated as follows. IP175A LF doesn't support tag VLAN function.

| Frame type of the              | The operation of a output port |                                                                                                                                                            |  |  |  |  |  |

|--------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| received packet                | Forward to a untagged filed    | Forward to a tagged field                                                                                                                                  |  |  |  |  |  |

| Untagged                       | Transmit as received           | <ol> <li>Insert VLAN tag to the packet.</li> <li>The inserted VLAN tag is defined in the<br/>EEPROM register of source port.</li> </ol>                    |  |  |  |  |  |

| Priority-tagged<br>(VLAN ID=0) | Strip tag                      | <ol> <li>Keep priority field.</li> <li>Modify the VLAN ID.</li> <li>The modified VLAN tag is defined in the<br/>EEPROM register of source port.</li> </ol> |  |  |  |  |  |

| VLAN-tagged                    | Strip tag                      | Transmit as received                                                                                                                                       |  |  |  |  |  |

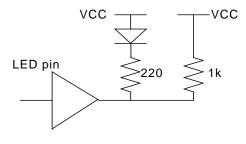

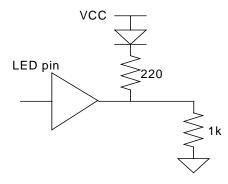

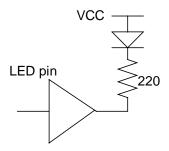

### 4.8 Initial value set by LED pins

Most configuration pins are shared with LED pin in IP175A LF. These multi-function pins are input during reset period and are LED output after reset. IP175A LF reads initial value via pins during the reset period. An initial value is set to 1 (0) by connecting a pin to vcc (gnd) through a  $10k\Omega$  ( $1k\Omega$ ) resistor as shown on the following figure.

The application circuit is shown below.

to set initial value = 1 with pull up 1k ohm resister to VCC

to set initial value = 0 with pull down 1k ohm resister to GND

to use default value (use no resistor to leave it open)

### 4.9 Built in regulator

IP175A LF built in a linear regulator to generate 2.15v power. The applications are shown below.

Pure switch with a 3.6v power adaptor.

Router with an on board 3.3v power source

Pure switch uses on board single power source

### 4.10 Extended MII registers

| MII            | ROM        | Function            | R/W | Description                                                                                                                                                                                                           | Default |

|----------------|------------|---------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| MII reg        | ister 12   | 2H (18D)            |     | ·                                                                                                                                                                                                                     |         |

| 12.15<br>12.14 | 2.1<br>2.0 | LED_SEL [1:0]       | R/W | Led_sel, LED mode selection. LED_SEL[1:0]=2'b00: LED mode 0, LED_SEL[1:0]=2'b01: LED mode 1, LED_SEL[1:0]=2'b10: LED mode 2, LED_SEL[1:0]=2'b11: LED mode 3 (default)                                                 | 2'b11   |

| 12.13          | 4.7        | X_EN                | R/W | X_en,<br>IEEE 802.3x flow control enable<br>This signal is used as pause_en for digital parts.<br>1: enable, 0:disable                                                                                                | 1       |

| 12.12          | 4.4        | BK_EN               | R/W | Bk_en, Backpressure enable 1: enable, 0: disable                                                                                                                                                                      | 1       |

| 12.11          | 4.2        | BF_STM_EN           | R/W | Broadcast storm enable 1: enable Drop the incoming packet if the number of queued broadcast packet is over the threshold. The threshold is defined in register 0AH[14:13]. 0: disable                                 | 0       |

| 12.10          | 4.3        | MAC_X_EN            | R/W | MII0 flow control enable 1: enable, 0: disable                                                                                                                                                                        | 1       |

| 12.7           |            | MII_REGISTER_<br>EN | R/W | select MII register     select EEPROM register  This bit should not be enabled until the contents of MII registers are all filled with correct value.                                                                 | 0       |

| 12.6           | B.4        | UPDATE_R4_EN        | R/W | Update_r4_en, Change capability enable A full duplex port will change its capability to half duplex, if the remote full duplex port does not support 802.3x and this function is enable. 1: enable, 0: disable        |         |

| 12.4           | 6.5        | Reserved            | R/W |                                                                                                                                                                                                                       | 0       |

| 12.3           | 6.4        | AGING               | R/W | Aging time, Aging time of address table selection An address tag in hashing table will be dropped if this function is turned on and its aging timer expires. Aging =bit[4] 0: no aging 1: aging time 300sec (default) | 1       |

| 12.2           |            | MII0_SPEED          | RO  | Speed of MII0 1: 100M 0: 10M It is speed of MII0 if P4_EXT is enabled. It is speed of port4 if P4EXT is disabled                                                                                                      | 0       |

| MII                    | ROM | Function | R/W | Description                                                                                                                       | Default |  |  |

|------------------------|-----|----------|-----|-----------------------------------------------------------------------------------------------------------------------------------|---------|--|--|

| MII register 12H (18D) |     |          |     |                                                                                                                                   |         |  |  |

| 12.1                   |     | MII0_FDX | RO  | Speed of MII0 1: full duplex 0: half duplex It is duplex of MII0 if P4_EXT is enabled. It is duplex of port4 if P4EXT is disabled | 0       |  |  |

| 12.0                   | 6.6 | Reserved | R/W |                                                                                                                                   | 0       |  |  |

| MII               | ROM      | Function | R/W | Description                                                                                                                                    | Default |

|-------------------|----------|----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| MII reg           | ister 13 | 3H (19D) |     |                                                                                                                                                |         |

| 13.15             | -        |          | R/W | Don't care                                                                                                                                     | 0       |

| 13.14             | E.6      | P0_COS   | R/W | Port0 Class of service enable 1: enable, 0: disabled (default) Packets with high priority tag from port0 are handled as high priority packets. | 0       |

| 13.13             | E.5      | P0_HIGH  | R/W | Port0 set to be high priority port 1: enable, 0: disabled (default) Packets received from port0 are handled as high priority packets.          | 0       |

| 13.12             |          | Reserved |     | Don't care                                                                                                                                     |         |

| 13.6              | F.6      | P1_COS   | R/W | Port1 Class of service enable 1: enable, 0: disabled (default) Packets with high priority tag from port1 are handled as high priority packets. | 0       |

| 13.5              | F.5      | P1_ HIGH | R/W | Port1 set to be high priority port 1: enable, 0: disabled (default) Packets received from port1 are handled as high priority packets.          | 0       |

| 13.4<br>·<br>13.0 |          | Reserved |     | Don't care                                                                                                                                     |         |

| MII     | ROM                    | Function | R/W | Description                                                                                                                                    | Default |  |  |

|---------|------------------------|----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|--|

| MII reg | MII register 14H (20D) |          |     |                                                                                                                                                |         |  |  |

| 14.15   |                        |          | R/W | Don't care                                                                                                                                     | 0       |  |  |

| 14.14   | 10.6                   | P2_COS   | R/W | Port2 Class of service enable 1: enable, 0: disabled (default) Packets with high priority tag from port2 are handled as high priority packets. | 0       |  |  |

| 14.13   | 10.5                   | P2_ HIGH | R/W | Port2 set to be high priority port 1: enable, 0: disabled (default) Packets received from port2 are handled as high priority packets.          | 0       |  |  |

| MII                    | ROM  | Function | R/W | Description                                                                                                                                    | Default |  |

|------------------------|------|----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|

| MII register 14H (20D) |      |          |     |                                                                                                                                                |         |  |

| 14.12                  |      | Reserved |     | Don't care                                                                                                                                     |         |  |

| l                      |      |          |     |                                                                                                                                                |         |  |

| 14.7                   |      |          |     |                                                                                                                                                |         |  |

| 14.6                   | 11.6 | P3_COS   | R/W | Port3 Class of service enable 1: enable, 0: disabled (default) Packets with high priority tag from port3 are handled as high priority packets. | 0       |  |

| 14.5                   | 11.5 | P3_ HIGH | R/W | Port3 set to be high priority port 1: enable, 0: disabled (default) Packets received from port3 are handled as high priority packets.          | 0       |  |

| 14.4                   |      | Reserved |     | Don't care                                                                                                                                     |         |  |

| ≀<br>14.0              |      |          |     |                                                                                                                                                |         |  |

| MII                    | ROM  | Function | R/W | Description                                                                                                                                    | Default |  |

|------------------------|------|----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|

| MII register 15H (21D) |      |          |     |                                                                                                                                                |         |  |

| 15.15                  |      |          | R/W | Don't care                                                                                                                                     | 0       |  |

| 15.14                  | 12.6 | P4_COS   | R/W | Port4 Class of service enable 1: enable, 0: disabled (default) Packets with high priority tag from port4 are handled as high priority packets. | 0       |  |

| 15.13                  | 12.5 | P4_ HIGH | R/W | Port4 set to be high priority port 1: enable, 0: disabled (default) Packets received from port4 are handled as high priority packets.          | 0       |  |

| 15.12                  |      | Reserved |     | Don't care                                                                                                                                     |         |  |

| <sup>≀</sup><br>15.0   |      |          |     |                                                                                                                                                |         |  |

| MII                                | ROM  | Function | R/W | Description                                                                                        | Default |  |

|------------------------------------|------|----------|-----|----------------------------------------------------------------------------------------------------|---------|--|

| MII register 16H (22D) is reserved |      |          |     |                                                                                                    |         |  |

|                                    | 13.4 | P4_FORCE | R/W | Port4 force mode enable 1: enable force mode 0: disable force mode, port4 NWAY with all capability | 0       |  |

|                                    | 13.3 | P3_FORCE | R/W | Port3 force mode enable 1: enable force mode 0: disable force mode, port3 NWAY with all capability | 0       |  |

|                                    | 13.2 | P2_FORCE | R/W | Port2 force mode enable 1: enable force mode 0: disable force mode, port2 NWAY with all capability | 0       |  |

|                                    | 13.1 | P1_FORCE | R/W | Port1 force mode enable 1: enable force mode 0: disable force mode, port1 NWAY with all capability | 0       |  |

| MII     | ROM      | Function            | R/W | Description                                                                                                                  | Default |

|---------|----------|---------------------|-----|------------------------------------------------------------------------------------------------------------------------------|---------|

| MII reg | ister 16 | 6H (22D) is reserve | ed  |                                                                                                                              |         |

|         | 13.0     | P0_FORCE            | R/W | Port0 force mode enable 1: enable force mode 0: disable force mode, port0 NWAY with all capability                           | 0       |

|         | 14.4     | P4_FORCE100         | R/W | Force port4 to be 100M 1: force to be 100M 0: force to be 10M It is valid only if p4_force (15h[15]) is set to 1'b1.         | 0       |

|         | 14.3     | P3_FORCE100         | R/W | Force port3 to be 100M 1: force to be 100M 0: force to be 10M It is valid only if p3_force (15h[14]) is set to 1'b1.         | 0       |

|         | 14.2     | P2_FORCE100         | R/W | Force port2 to be 100M 1: force to be 100M 0: force to be 10M It is valid only if p2_force (15h[13]) is set to 1'b1.         | 0       |

|         | 14.1     | P1_FORCE100         | R/W | Force port1 to be 100M 1: force to be 100M 0: force to be 10M It is valid only if p1_force (15h[12]) is set to 1'b1.         | 0       |

|         | 14.0     | P0_FORCE100         | R/W | Force port0 to be 100M 1: force to be 100M 0: force to be 10M It is valid only if p0_force (15h[11]) is set to 1'b1.         | 0       |

|         | 15.4     | P4_FORCE_FULL       | R/W | Force port4 to be full duplex 1: force full duplex 0: force half duplex It is valid only if p4_force (15.15) is set to 1'b1. | 0       |

|         | 15.3     | P3_FORCE_FULL       | R/W | Force port3 to be full duplex 1: force full duplex 0: force half duplex It is valid only if p4_force (15.14) is set to 1'b1. | 0       |

|         | 15.2     | P2_FORCE_FULL       | R/W | Force port2 to be full duplex 1: force full duplex 0: force half duplex It is valid only if p4_force (15.13) is set to 1'b1. | 0       |

|         | 15.1     | P1_FORCE_FULL       | R/W | Force port1 to be full duplex 1: force full duplex 0: force half duplex It is valid only if p4_force (15.12) is set to 1'b1. | 0       |

|         | 15.0     | P0_FORCE_FULL       | R/W | Force port0 to be full duplex 1: force full duplex 0: force half duplex It is valid only if p4_force (15.11) is set to 1'b1. | 0       |

| 16.0    |          |                     |     | Reserved                                                                                                                     |         |

| MII       | ROM      | Function        | R/W | Description                                                                                                           | Default |

|-----------|----------|-----------------|-----|-----------------------------------------------------------------------------------------------------------------------|---------|

| MII reg   | ister 17 | 7H (23D)        |     |                                                                                                                       |         |

| 17[15:11] | 16[4:0]  | Add VLAN tag    | R/W | Add VLAN tag 17H[11] 1: port0 adds a VLAN tag to each outgoing packet. 0: port0 doesn't add a VLAN tag.               | 5'b0    |

|           |          |                 |     | 17H[12] 1: port1 adds a VLAN tag to each outgoing packet. 0: port1 doesn't add a VLAN tag.                            |         |

|           |          |                 |     | 17H[13] 1: port2 adds a VLAN tag to each outgoing packet. 0: port2 doesn't add a VLAN tag.                            |         |

|           |          |                 |     | 17H[14] 1: port3 adds a VLAN tag to each outgoing packet. 0: port3 doesn't add a VLAN tag.                            |         |

|           |          |                 |     | 17H[15] 1: port4 adds a VLAN tag to each outgoing packet. 0: port4 doesn't add a VLAN tag.                            |         |

| 17[10:6]  | 17[4:0]  | Remove VLAN tag | R/W | Remove VLAN tag 17H[6] 1: port0 removes the VLAN tag from each outgoing packet. 0: port0 doesn't remove the VLAN tag. | 5'b0    |

|           |          |                 |     | 17H[7] 1: port1 removes the VLAN tag from each outgoing packet. 0: port1 doesn't remove the VLAN tag.                 |         |

|           |          |                 |     | 17H[8] 1: port2 removes the VLAN tag from each outgoing packet. 0: port2 doesn't remove the VLAN tag.                 |         |

|           |          |                 |     | 17H[9] 1: port3 removes the VLAN tag from each outgoing packet. 0: port3 doesn't remove the VLAN tag.                 |         |